Binary Clock, update 2

This is an update on my binary clock project. Click here for the previous post

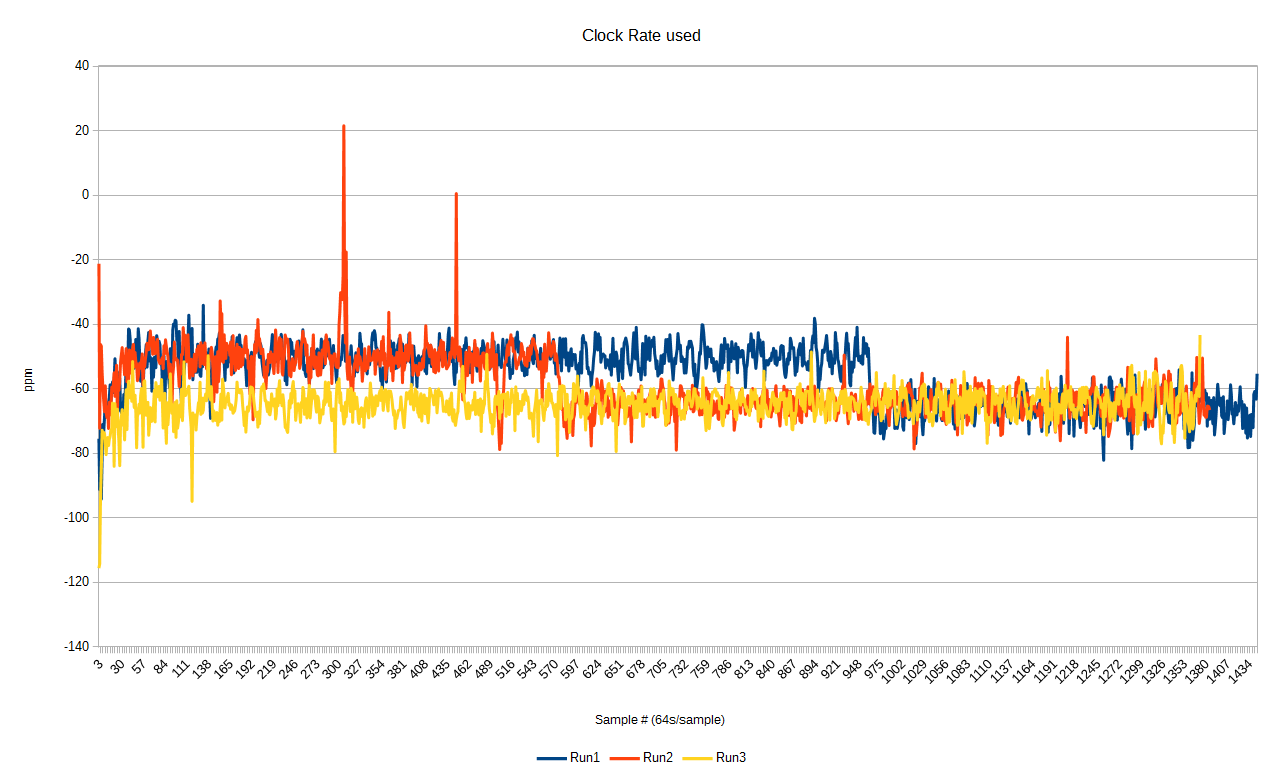

I've been working on a PID controller to adjust the local clock's rate. Right now, it's just a simulation running on my PC using the data from the esp8266 module. I like the PID controller for this because the largest source of clock error is the rate difference (the derivative term). I can measure the rate difference between the local clock and the upstream clock using a linear regression.

This graph shows three runs, each over 24 hours. The rate used was mostly stable within +/- 10 ppm. At the start, the rate changes quickly to lower the offset between the two clocks. After the offset is low enough, the rate changes relatively slowly.

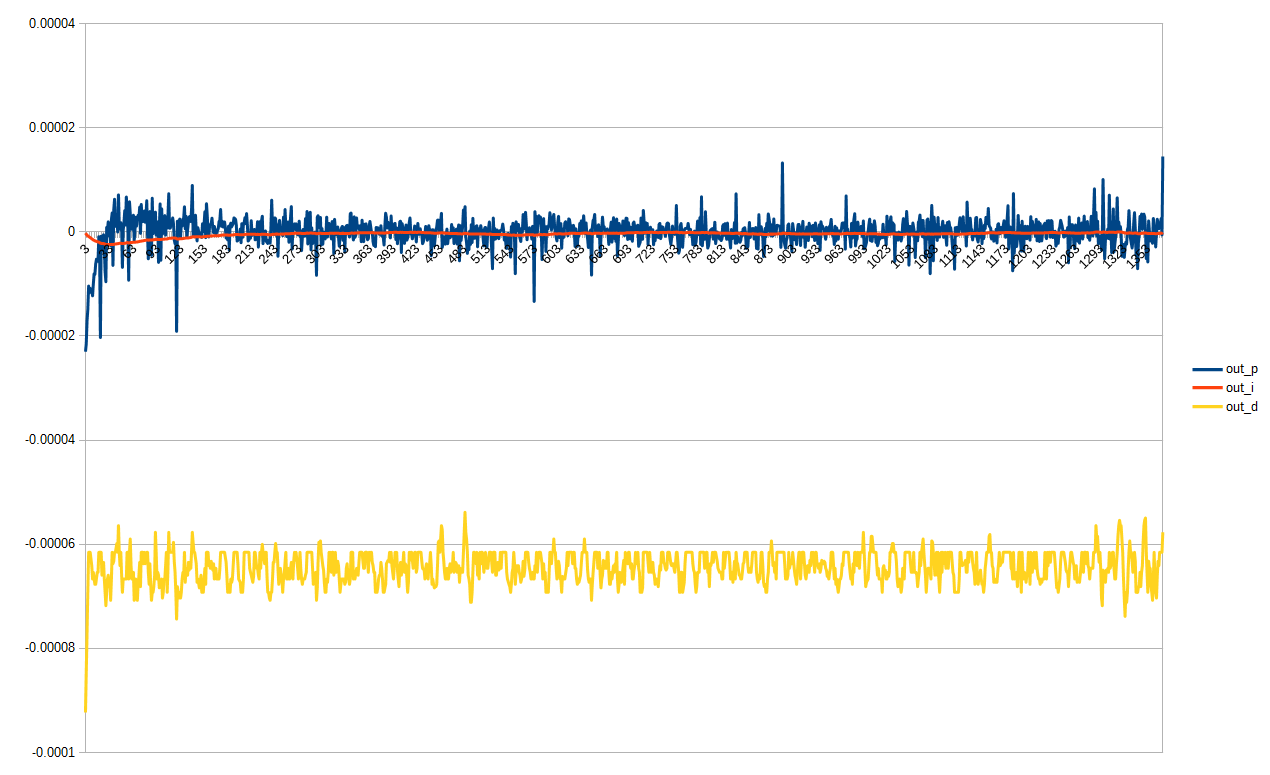

Looking into the individual terms in the PID output of the third run:

You can see the P (immediate offset) and I terms (accumulated offset) quickly settle after getting rid of the initial offset between the clocks. The D term (rate difference) stays around -70ppm.

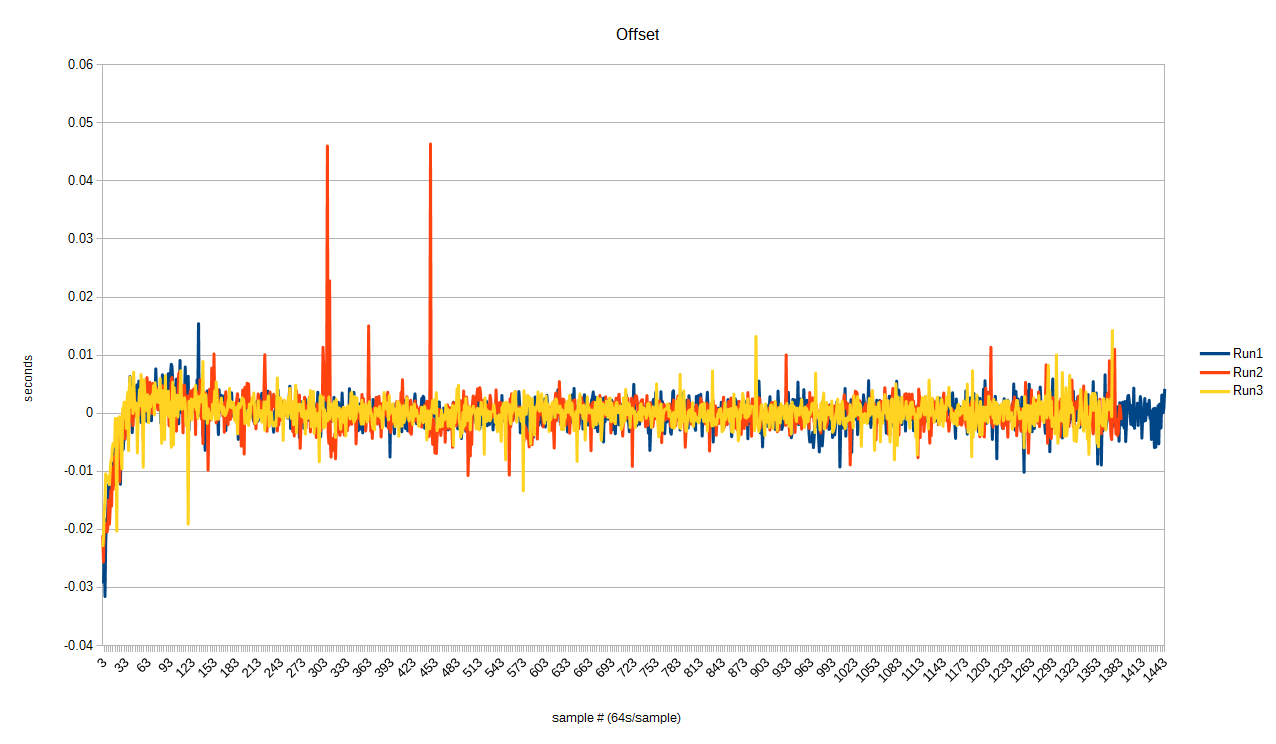

And the results:

The 1st and 99th percentiles for these offsets are -11ms and +6ms. This meets my goal of "within tens of milliseconds of true time".

Questions? Comments? Contact information